# 逢甲大學學生報告 ePaper

# 報告題名:

# MOS 的 Surface potential 之探討

作者:蕭名凱 俞詠騰 李茂瑜

系級:電子四甲

學號: D9465722 D9465871 D9465909

開課老師:李景松 老師

課程名稱:化合物半導體元件

開課系所:電子工程系

開課學年:97學年度 第一學期

# 摘要

目前 MOSFET 被廣泛應用於在數位電路的應用之中,這是因其 具有相當小的面積,而且能製造數千個元件於單一個積體電路之上。 所以無庸置疑的, MOSFET 是目前積體電路設計的核心。 MOSFET 的心臟是一個稱為 MOS 電容的金屬-氧化物-半導體結構。當在 MOS 電容上外加一個電壓時,在半導體之中接近氧化物-半導體界 面的能帶將會彎曲。在氧化物-半導體界面處,傳導帶及價帶相對於 費米能階的位置是 MOS 電容器電壓的一個函數,因此我們能夠藉由 外加適當的電壓而將半導體的表面特性由p型反轉成n型,或者由n 型反轉成p型。MOSFET的操作及特性乃是由半導體表面處的這種反 轉,以及所產生的反轉電荷密度所決定的。臨限電壓(threshold voltage)被定義為產生反轉層電荷所需要外加的閘極電壓,為 MOSFET 的一個重要係數。因表面電位於整個 MOSFET 的影響極廣, 故我們主要於探討當"閘極殿壓"=="臨界電壓"時, 臨界反轉點的 MOS 表面電位.

關鍵字:表面電位,MOS,FET。

# 目錄

| 摘- | 要i                       |

|----|--------------------------|

| 目釒 | 錄ii                      |

| —  | 、MOSFET基礎4               |

|    | 1-1 場效電晶體簡介4             |

|    | 1-2 金氧半場效電晶體的構造、原理與特性6   |

|    | 1-3 金氧半場效電晶體的應用17        |

| 二  | 、MOS通道一維表面電位分析           |

|    | 2-1 表面電位概說及計算22          |

|    | 2-2 臨限電壓的求得24            |

|    | 2-3 表面電位相關推導             |

|    | 2-4 表面電位之繪圖與探討錯誤!尚未定義書籤。 |

| 三  | 、MOS通道二維電位描述29           |

|    | 3-1 改變VG29               |

|    | 3-2 改變L對表面電位的影響30        |

|    | 3-3 N通道改變NA摻雜量34         |

| 結 | 論. |    |    | <br> | <br> | • • | <br> |  | <br> | <br> | . <b>.</b> . | <br> | <br> | • | <br> | • | <br> |  | <br>. 3 | 7 |

|---|----|----|----|------|------|-----|------|--|------|------|--------------|------|------|---|------|---|------|--|---------|---|

| 參 | 考  | 資う | 料. | <br> | <br> |     | <br> |  | <br> | <br> |              | <br> | <br> |   | <br> |   | <br> |  | <br>. 3 | 8 |

# 一、MOSFET 基礎

### 1-1 場效電晶體簡介

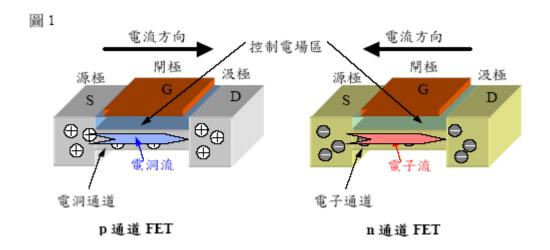

一般場效電晶體 (field effect transistor, 簡稱 FET) 和雙極電晶 體一樣都有三隻接腳,不過工作原理卻完全不同。FET 的控制接腳稱 為閘極(gate,簡稱 G 極),顧名思義閘極的功用就如同水壩的閘門; 而水壩上方的水庫可以提供水,對應到 FET 的另一接腳稱做源極 (source,簡稱 S 極);水壩下方水的出口,對應到 FET 的第三隻腳 稱為汲極 (drain, 簡稱 D 極)。而水流就可以對應到電流,不過半 導體中的電流可以是電子流或電洞流,利用電子流來工作的稱為 n 通 道場效電晶體 (n-channel FET),利用電洞流來工作的稱為 p 通道場 效電晶體 (p-channel FET)。n 通道 FET 的源極提供電子,經過n型 通道(channel),到達汲極,電流方向是由汲極流向源極;p通道FET 的源極則提供電洞,經過p型通道(channel),到達汲極,電流方向 是由源極流向汲極。通道的特性和其附近的電場有關,該電場可由閘 極的電位來控制,故此類電晶體稱為場效電晶體。圖 1 為 n 和 p 通 道 FET 的示意圖。由於 FET 工作時只利用到多數載體,和少數載體 的特性無關,故均屬於單載體元件(unipolar devices)。

#### 圖 1、n和p通道 FET 的結構比較圖

FET的構想在BJT被發明前就有了,只是那時材料及材料間介面 缺陷都無法控制,一直沒有實用的FET結構出現。近年來由於材料及 磊晶技術的進步,我們可以將材料及介面的缺陷及雜質降得很低, FET得到很大的發展。

FET 的種類除了依導通用的載體種類來分外,還可依照閘極的結構來分。FET 閘極結構有很多種類,這裡介紹兩種最常見的,一是逆向偏壓的 pn 接面,另一種是閘極金屬、絕緣氧化物和半導體形成類似電容的結構。前者稱為接面場效電晶體(junction field effect transistor,簡稱 JFET),後者稱為金氧半場效電晶體(metal-oxide-semiconductor field effect transistor,簡稱 MOSFET)。而後者 MOSFET 也是我們主要要討論的重點。

### 1-2 金氧半場效電晶體的構造、原理與特性

MOSFET應該是人類使用最多的電晶體種類,特別是在電腦及通訊相關的電子設備中,大量的這種電晶體開關幫助我們處理、運算及記憶大量的數據。由於 MOSFET 的結構特別適合被縮小化,而且功率需求也小,在同一晶片上製作上千萬個電晶體開關變得可行。

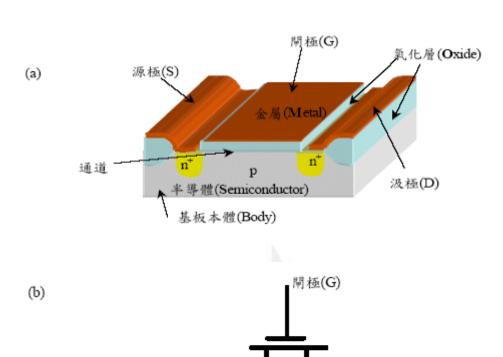

MOSFET控制通道的方式和JFET不同,但元件特性有許多相同之處。這裡我們以n通道MOSFET (簡稱NMOS)為例來介紹他的構造與原理。圖2(a)為一典型的NMOS的結構示意圖。開極是由金屬、氧化層和半導體依序疊在一起所形成類似電容的結構(氧化層當做介電質),故命名為金氧半場效電晶體。開極只要加上足夠的正電壓,即可在半導體內靠近氧化層的介面上,吸引足夠多的導電電子形成通道,使源極與汲極的n+區導通。故控制開極的電壓,等效上就是控制氧化層內的電場,就可以控制源極與汲極之間的導電特性。基板本體(body)有時也會接出一隻腳,使MOSFET變成四隻腳的元件,在大部分的應用中,基板本體會和源極接在一起,使源極、汲極和基板本體間的pn接面永遠是不導通的,如此MOSFET就變成和JFET類似的三隻腳元件。圖2(b)包括三隻接腳與四隻接腳的NMOS電路符號。

圖2、(a)為一典型的NMOS 的結構示意圖。(b)包括三隻接腳與四隻接腳的NMOS電路符號。

源極(S)

由於 MOSFET 中,導電電子是在靠近介面的通道運動,因此氧化層與半導體接面必須製作得非常平整。現代的半導體技術能夠在矽晶圓的表面形成結構緻密的二氧化矽 (SiO2)層,而且介面的品質可以有效地被控制,故常用的 MOSFET 元件均是以矽晶圓做基板材料。

下面我們將較仔細的介紹n 通道MOSFET 的工作原理以及元件 在不同偏壓情形的變化。

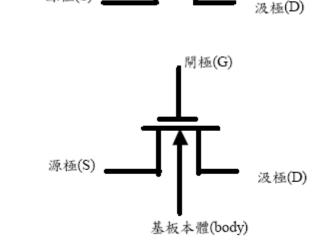

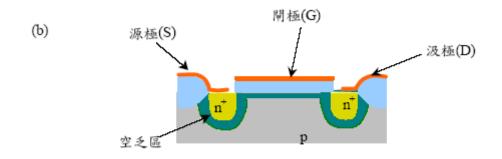

當閘極沒加偏壓(相對於基板本體或與之連結之源極),源極與 汲極間只是像兩個反向串接的 pn 接面,互不導通,NMOS 在所謂的 截止(cut off)狀態,如圖 3(a),其中還顯示了 n+型源極與汲極各和 p 型基板間 pn 接面的空乏區。

圖 3、不同閘極偏壓下,空乏區與通道形成之示意圖。(a)VGS=0,(b) VGS=Vth,(c) VGS=Vth,(d) VGS>Vth。

在閘極與基板本體(和源極相接)間慢慢加上正電壓,由於閘極的結構類似電容,閘極的金屬導體會堆積一些正電荷,而在氧化物絕緣層另一邊,則會吸引等量的負電,我們可以看成是吸引了導電電子,但電子在很短時間內即被多數載體電洞復和了,或者是電洞被閘極的正電荷趕跑了,不管哪一種看法,結果都是在靠近氧化層的p型半導體內形成空乏區,所帶的負電都來自電洞被游離的受子摻雜,如圖3(b),這裡先討論汲極與源極電位差很小的情形。源極與汲極間仍然不導通,NMOS 在截止區。

如果閘極的正電壓持續增加,到達一特定的臨限電壓 Vth,在氧 化層與半導體的介面會開始出現導電電子層,如圖 3(c)。以後再增加 的閘極電壓就不再用來改變空乏區的大小,而是用來增加導電電子層的電子數目,如圖 3 (d)。這時源極與閘極可藉由此導電電子層形成之通道導通。由閘極的電壓變化,可以將原本 p 型半導體,轉變成具導電電子的 n 型通道,此導電通道我們稱為反轉層 (inversion layer)。

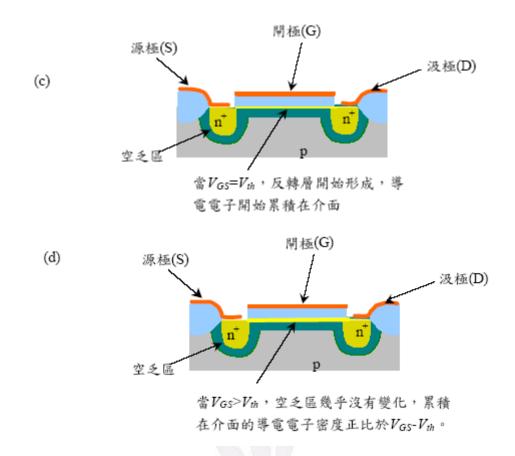

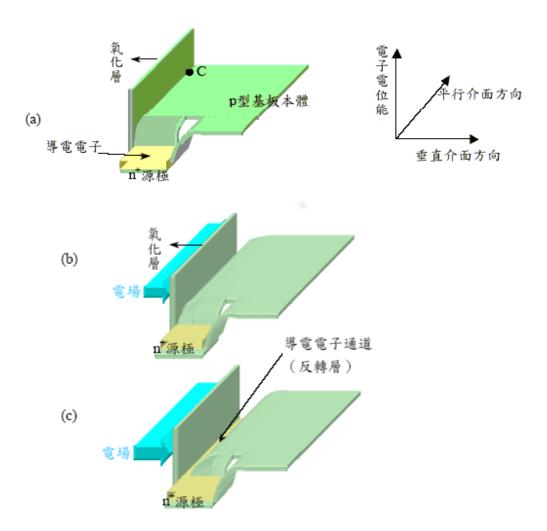

間極電壓加到什麼程度反轉層才會形成呢?這必須考慮在半導體靠近氧化層介面的電子電位能受到閘極電壓影響產生的變化。假設沒有加閘極電壓時,氧化層和半導體中均無電場,電子在p型半導體中(遠離源極和汲極處)的電位能分佈應是平的,如圖4(a),圖中z軸方向代表電子電位能,另兩軸是標示在半導體中的位置。電子不喜歡處在氧化層中,也就是說那裡的電位能較高,故在進入氧化層的介面上有一個像牆一樣很高的位障,阻止電子進入氧化層。靠近源極或汲極的n+半導體處,電子電位能較在p型半導體中為低。圖4只畫出靠近源極附近的電位能分佈狀況,在汲極和源極電位差不大的情形下,在汲極附近的電位能分佈狀況也類似。介面通道區的電子電位能太高,導電電子被侷限在源極與汲極的n+區,不能互相導通。

對閘極開始加正電壓時,氧化層中會有一朝向半導體基板的電場,如圖 4 (b)所示,電子在閘極金屬的電位能會變低,靠近介面的 p型半導體區的電子電位能也會被往下拉,電位能面彎曲的部分就是空 乏區的部分。 圖 4、NMOS 中,對於不同閘極偏壓,電子電位能在半導體中的分佈 圖。(a)VGS=0,(b) VGS<Vth,(c) VGS>Vth。導電電子無法進入氧化 層,故氧化層用一極高的位障表示。

當閘極的電壓足夠高,即超過 Vth 時,靠近介面的半導體區的電子電位能會下降到使源極 (n+區) 中的導電電子能夠流入通道區,如圖 4(c)所示,形成反轉層,源極與汲極間遂能導通。

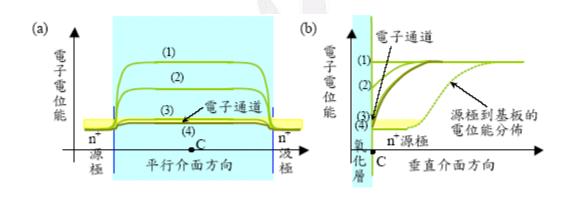

圖 5(a)是在不同的閘極偏壓,靠近氧化層的半導體中,電子電位 能沿著源極、通道中點 C 到汲極的分佈改變;圖 5(b)則是由 C 點、 沿著和介面垂直方向,朝向基板方向的電子電位能變化,虛線是由源 極到 p 型半導體基板的電位能變化。通道中點 C 在圖 3(a)及 4(a)中也有標出來。從圖 5 中很容易看出通道區和源極電子電位能的差別,而開極電壓就是用來調整在氧化層與半導體介面通道的電子電位能。 圖 5、NMOS 中,對於不同閘極偏壓,電子電位能在半導體中,(a)沿著源極、通道中點 C 到汲極,以及(b)由 C 點、沿著和介面垂直方向,朝向基板方向的分佈圖。(1)VGS=0,(2) VGS<Vth,(3) VGS=Vth,(4) VGS>Vth。(b)中之虛線是由源極到 p 型半導體基板的電位能變化。

這裡還有一點要說明,在 VGS 超過 Vth 後,再增加的電壓除了持續在閘極金屬層有正電荷儲存外,在半導體區也必須增加等量的負電荷,由於此時反轉層已形成,負電荷很容易由源極進入通道,所費之能量遠較改變空乏區產生負電荷來得小,因此空乏區寬度就不再變化了。

瞭解了NMOS 的基本工作原理,下面我們可以開始討論他的電

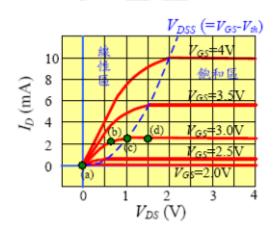

流電壓的特性。圖6是不同閘極偏壓(VGS)的ID對VDS曲線,這個圖例中NMOS的臨界電壓Vth為2V。當VGS>Vth時,源汲極間開始導通,考慮源極和汲極電位差不大的情形,反轉層的電子密度約和(VGS-Vth)成正比,因此通道的電阻和(VGS-Vth)成反比,故在VDS很小的區域,ID對VDS的關係幾乎為一條直線,而且對相同的VDS,(VGS-Vth)愈大則導電電子愈多,ID愈大。

圖 6、不同閘極偏壓(VGS)的 ID 對 VDS 曲線,這個 NMOS 的臨界 電壓 Vth 為 2V。

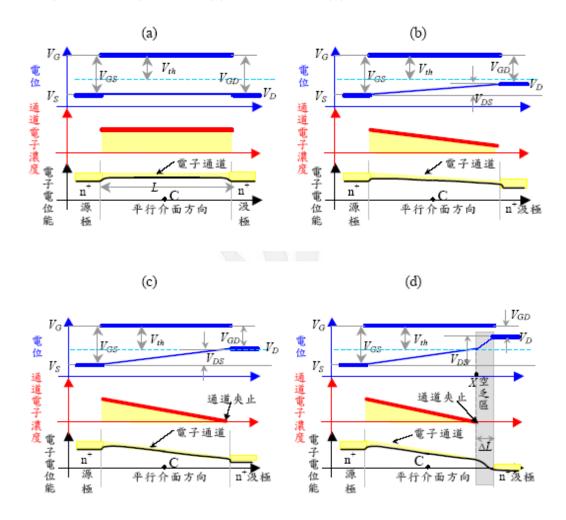

當 VDS 變大時,和 JFET 的情形類似,ID 對 VDS 的曲線也會向下彎,原因和 JFET 也有類似之處。考慮 VGS 固定在 3V 的情形, VDS 很小時,整個通道上的電位差不多,閘極金屬到通道上任一點的電位差也都一樣,通道上的導電電子密度分佈很均勻,如圖 7 (a)所示。圖 7 是當 VGS(>Vth)固定時,對於不同 VDS,沿著通道的電位、

導電電子濃度及電位能變化曲線。

圖 7、當 NMOS 之 VGS(>Vth)固定時,對於不同 VDS,沿著通道的電位、導電電子濃度及電位能變化曲線。(a) VDS=0,(b)

VGD(=VGS-VDS)>Vth, (c) VGD=Vth, (d)VGD<Vth

當 VDS 增大時,通道上的電位會由源極向汲極方向變高,開極金屬到通道的電位差在靠近汲極處較小,因此在靠近汲極處通道的導電電子密度變小。圖 7(b)是 VGD(=VGS-VDS)> Vth 的情形,靠近汲極的通道電子密度較小,整個通道的電阻較 VDS 很小時為大,故 ID 對 VDS的曲線會向下彎曲。當 VGD= Vth,如圖 7(c),最靠近汲極的反轉層消

失,通道被夾止。如果 VDS 繼續增加,VGD 變得比 Vth 小,靠汲極被夾止的區域 L 會略微變大,形成空乏區,但 L << L,如圖 7(d) 所示,反轉層消失的點 X 的電位符合 VGX = Vth,和 VDS 無關,也就是說反轉層兩端之電位差 VXS 不隨 VDS 改變,而且反轉層之電子濃度分佈與尺寸大小也不隨 VDS 改變,故通過之電流 ID 不隨 VDS 改變。靠近汲極通道夾止後再增加的 VDS,大部分都落在被夾止部分的空乏區,電子電位能到此區也會有一個很大的下降,導電電子到此區會被加速掃到汲極。

圖6中標示 VGS=3.0V 的曲線上,標有(a)、(b)、(c)與(d)四點,分別對應圖7中相同編碼圖形的偏壓情形。(a)和(b)的偏壓並不會使反轉層消失,通道和電阻類似,ID 隨 VDS 增加,稱為歐姆區或線性區;在 VDS 比(c)點大的區域,ID 幾乎不隨 VDS 改變,稱為飽和區或恆流區。歐姆區與飽和區的交界電壓 VDSS 必需符合 VGD=VGS-VDSS = Vth,即 VDSS=VGS-Vth, VDSS 隨 VGS 變大,如圖6中之虛線。

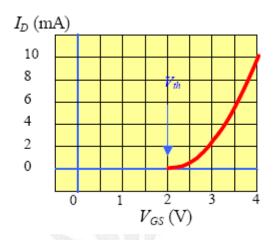

和 JFET 類似,MOSFET 是利用閘極偏壓控制源汲極間導通特性的元件,而且兩者之電特性也十分相像,不過一般而言 MOSFET 的閘極漏電流會比 JFET 小。圖 8 是 NMOS 在飽和區的典型轉換特性曲線。跟 JFET 比較下,我們可以發現 JFET 在沒加偏壓(VGS =0)時是導通的,而 NMOS 在沒加偏壓時是不導通的。通常我們稱前者為空

乏型 (depletion mode) FET,因為要改變現有導通的狀況,必須在閘極施加偏壓,使得通道被"空乏"掉;後者則稱為增強型

(enhancement mode) FET,因為要改變現有導通的狀況,必須在閘極施加偏壓,使得通道被"增強"出來。

圖 8、NMOS 在飽和區的典型轉換特性曲線。

MOSFET 也可以設計成空乏型的元件,只要製作時在靠近介面的半導體中直接摻雜製作出通道,例如 NMOS 就加入 n 型摻雜即可,如此在沒閘極偏壓時元件是在導通的狀態。JFET 則無法做出增強型的元件。

p 通道 MOSFET (簡稱 PMOS) 原理和 NMOS 相同,但偏壓及電流方向則相反。PMOS 的主要導通載體為帶正電的電洞,因此閘極必須加上足夠負,或比臨界電壓小的電壓,才能夠在通道區吸引足夠的電洞形成反轉層,使源極和汲極導通。電洞是由源極,經通道,流向汲極,電流方向也是一樣,故源極的電位應較汲極低。

### 1-3 金氧半場效電晶體的應用

FET 和 BJT 一樣,可以用作開關或放大器,利用閘極的電壓訊號,控制源極和汲極間的電流。JFET 和 MOSFET 使用的場合略有不同。JFET 可用作類比開關及訊號放大器,特別是低雜訊的放大器,但很少用在數位電路中的邏輯運算及功率放大器;MOSFET 用途較廣,除一般的開關、訊號放大及功率放大器外,在數位電路及記憶體等大型積體電路(VLSI)方面,都是 MOSFET 的天下,特別是將 NMOS及 PMOS 製作在同一晶圓,稱做 CMOS (complementary MOS) 的技術,或稱互補式金氧半電晶體技術。

FET 應用在類比訊號放大器的設計方法和BJT 相當類似。對應BJT 的共射極、共基極和共集極的接法,FET 也有共源極、共閘極和共汲極的接法。FET的汲極不能當作輸入端,閘極不能當輸出端,和BJT 集極與基極的限制也一樣。此外,FET 應該偏壓在飽和區(或恆流區),閘極的電訊號疊加在原來之直流偏壓電壓上,造成輸出電流ID 的變化。

有關MOSFET 在數位電路的應用,我們這裡介紹兩個簡單且具有代表性的電路,一個是CMOS 的反閘(NOT gate),他是一種數位邏輯閘(logic gate),功用是輸入是數位訊號"1"時,輸出是"0";數入是"0"時,輸出是"1"。另一個是電腦必備的動態隨機存取記

憶體(dynamic random-access memory, DRAM)的一個記憶胞(memory cell),就是一個能夠記憶"1"或"0"的電路單元。

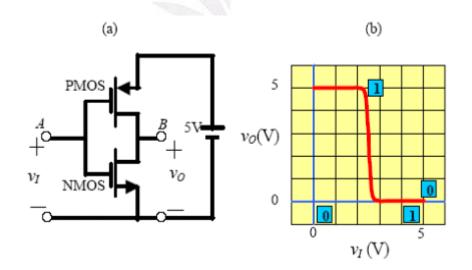

CMOS 反閘反閘是一個很基礎的邏輯運算,可以用BJT 來做,也可以用NMOS 來做,但均不如CMOS 的電路來的簡潔,而且以功率消耗而言,CMOS 電路更是優越。圖9(a)是一個由NMOS 和PMOS 串接的一個CMOS 電路,二者閘極連結在一起當作輸入端VI,汲極接在一起做輸出端VO,提供電路兩端5V的直流電源。

圖9、(a)一個由NMOS 和PMOS 串接的一個CMOS 反閘電路,(b) vO 對 vI 的轉換特性曲線。

假設NMOS 的臨限電壓是2V,而PMOS 的是-2V。當輸入端為邏輯訊號" 0",即電壓訊號0V,對NMOS 而言,VGSN=0V < Vth=2V,在截止區,沒有電流通過;對PMOS 而言,VGSP=-5V < Vth=-2V,在導通狀態,

但通過的電流為0,故在線性區,且PMOS 源極和汲極間的電位降為0,故輸出電壓VO 為5V,相當於邏輯訊號"1"。當輸入端為邏輯訊號"1",即電壓訊號5V,對PMOS 而言,VGSP=0V>Vth=-2V,在截止區,沒有電流通過;對NMOS 而言,VGSN=5V>Vth=2V,在導通狀態,但通過的電流為0,故在線性區,且NMOS 源極和汲極間的電位降為0,故輸出電壓VO 為0V,相當於邏輯訊號"0"。

圖9(b)是這個電路VO對VI的轉換特性曲線,圖中可以看出輸入在0V附近一定範圍輸出為5V,輸入在5V附近則輸出為0V,合乎反閘的邏輯運算要求。另外有一點要注意的,當輸入無訊號變化時,也就是電晶體並無改變導通之狀態,通過兩個電晶體的電流均為0,故沒有功率損耗。功率損耗只發生在輸入有"0"和"1"之間變化的時候。

### 動態隨機存取記憶體

DRAM 是由矩陣式排列的記憶胞組成,一個DRAM 的晶片上會有很多矩陣,只要適當的安排地址,就很容易可以直接找到對應的記憶胞。所謂"隨機存取",是相對於早期,例如磁帶類型的記憶元件,必須依序一個個的把記憶取出的方式。"動態"的意義則是指這個記憶體必須常常去"更新"或"提醒"(refresh),也就是記憶不太好,記憶時間太長會容易有錯誤。

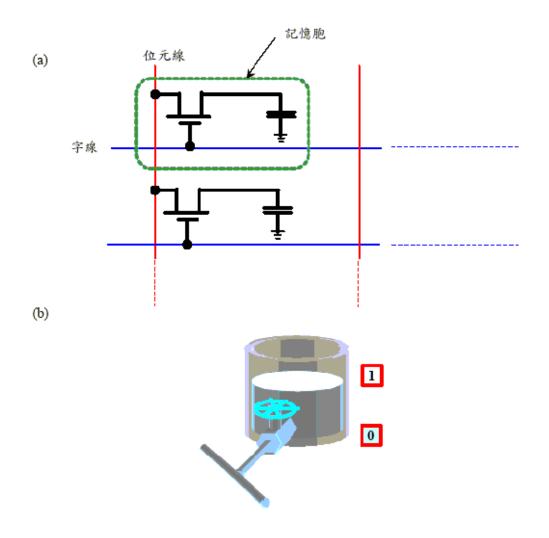

圖10、(a)DRAM 的一部份,虛線框起來的是一個基本記憶胞;(b)一個DRAM 的記憶胞可以類比成容器和閥的系統,電容相當於裝水的容器,NMOS 開關就相當於水閥。

DRAM 的記憶胞基本上就是一個電容加上一個控制充放電及讀取的電晶體開關,如圖10(a)所示。這裡用的是NMOS,但是源極和汲極並沒特別標出,主要原因是他是用作雙向開關,電流可以流入或流出電容。每一個記憶胞會外接兩條線,一條是控制閘極的稱字線(word

line),加上正電壓時可以選擇同一行的記憶胞(同一個字的不同位元),將他們的NMOS 開關導通;另一條接到源/汲極的稱為位元線(bit line),用來"寫"或"讀"資料到記憶胞中。所謂"寫"資料,是指當控制開關導通時,電容可以充電或放電,使得位元線的電壓訊號和電容兩端的電壓是一樣的。當控制開關不導通,電容便維持(記憶)他被"寫"入的電位,通常高電位為數位資料"1",接近OV的電位為數位資料"0"。要"讀"的時候,將控制開關打開,這時位元線則接到一個類似電位計的電路,即可讀出電容儲存的訊號。由於電路中的電容的正負電極間有漏電流,經一段時間就必須"更新"一下資料。

一個DRAM 的記憶胞可以類比成如圖10(b)的容器和閥的系統,電容相當於裝水的容器,水位到一定的高度就當作"1",幾乎沒水就是"0"。NMOS 開關就相當於水閥,控制水是否流通。要寫入"1"時就將閥門打開,水加適當的壓力注入容器,寫"0"則將水放掉。到讀記憶的資料,就將閥打開,讀一下水壓即可。

# 二、MOS 通道一維表面電位分析

### 2-1 表面電位概說及計算

表面電位(surface potential)ys是本體半導體之中所量測到的Eni(本微費米能階)以及在半導體表面所量測到的Eni兩者之間的差。 其乃是跨降在空乏電荷層的位勢差。

(本微費米能量)是位於接近禁止能帶隙中央的位置。我們可以明確 地計算本微費米能量的位置。由於電子與電洞的濃度相等,此表示式 為:

$N_c \exp[-(E_c - E_{fi})/kT] = N_v \exp[-(E_{fi} - E_v)/kT]$ 中隙能量定義為:

$$E_{fi} - E_{midgap} = (3/4) kT ln [m_p^*/m_n^*]$$

在閘極電壓等於臨限電壓時,表面電位Ys=2fF,電位fF是EFI與EFI (費米能階)之間的差。而此時的空乏區寬度W我們可以以一個類 似於單邊pn接面的型式來表示:

$$\mathbf{w} = \sqrt{\frac{2 \, \epsilon_{\mathrm{S}} \, (\psi_{\mathrm{S}} + \mathbf{V}_{BG})}{q \, \mathbf{N}_{A}}}$$

式子中es是半導體的電容率,Vxx是本體端的電壓,Nx則是施體的摻雜濃度。

在知道這些之後,我們就可以實際來計算所要的表面電位及空乏 區寬度的值了。以下是我們用 mathematica 實際做出的程式及結果:

#### MOS 的 Surface potential 之探討

$$\begin{split} \varepsilon_{S} &= (11.7) \ (8.85\,10^{\circ}-14) \ ; \\ V_{BG} &= 2 \ ; \\ q &= 1.6\,10^{\circ}-19 \ ; \\ N_{A} &= 10^{\circ}16 \ ; \\ n_{i} &= 1.5\,10^{\circ}10 \ ; \\ V_{t} &= 0.0259 \ ; \\ \phi_{F} &= V_{t} \ \text{Log} \Big[ \frac{N_{A}}{n_{i}} \Big] \\ \psi_{min} &= 2 \ \phi_{F} \\ W &= \sqrt{\frac{2 \ \varepsilon_{S} \ (\psi_{min} + V_{BG})}{q \ N_{A}}} \end{split}$$

- 0.34732

- 0.69464

- 0.0000590568

ymin:指ys,ni:本微載子濃度,Ve:熱電壓

長度單位:cm

(我們所用的設定數據均是用本專題最後所附的參考資料上的數據,以方便對照查證。)

如此我們即可求得所要的表面電位及空乏區寬度的值。但這只是個開始,因為在 MOS 的表面,其表面電位是會變動的,絕不可能是我們求得的這個定值,所以我們還要以其他方法來求得表面電位,再與現在已求得的來對照結合,以獲取最正確的結果。

### 2-2 臨限電壓的求得

臨限電壓(threshold voltage)被定義為是為了達到臨限反轉點所需要外加的閘極電壓。我們要探討在臨限電壓時 MOS 的表面電位分佈,就必須知道在我們設定的情況下臨限電壓的值,即我們必須知道臨限電壓的表示式。

臨限電壓<sup>№</sup>是半導體摻雜、氧化物電荷以及氧化物厚度的一個函數,我們可將它寫為:

$$V_{T} = \frac{Q_{SD} (max)}{C_{OX}} + V_{FB} + \psi_{S}$$

Q<sub>SD</sub> (max): 空乏區每單位面積的最大空乏電荷密度的大小

Cox:每單位面積的氧化物電容, VBB:平帶電壓

而對一個均勻摻雜的基板而言, 臨限電壓更可被寫成:

$$V_{T} = \frac{\sqrt{2 \epsilon_{S} q N_{A} (\psi_{S} + V_{BG})}}{C_{ov}} + V_{FB} + \psi_{S}$$

再經過短通道修正後,可以得到最終的臨限電壓表示式:

$$\begin{split} &V_T = V_{FB} + \psi_S + \frac{t_{ox}}{\varepsilon_{ox}} \; \sqrt{\; 2\,\varepsilon_S \; q \; N_A \; (\psi_S + V_{BG}) \; } \; \left(1 - \eta_0 \; \text{Exp} \big[ \frac{-L}{l_0} \; \big] \right) \\ &\eta_0 = \frac{\varepsilon_{ox}}{\varepsilon_S} \; \frac{\sqrt{\; (V_D + V_{bi} - \psi_S) \; (V_{bi} - \psi_S) \; } }{\psi_S + V_{BG}} \; \left( \frac{1}{t_{ox}} \; \sqrt{\; \frac{2\,\varepsilon_S \; (\psi_S + V_{BG})}{q \; N_A} \; } \; + \frac{3}{2} \; \frac{\varepsilon_S}{\varepsilon_{ox}} \right) \\ &l_0 = \sqrt{\; \frac{2\,\varepsilon_S \; (\psi_S + V_{BG})}{q \; N_A} \; } \; \left( \frac{3}{2} + \frac{1}{t_{ox}} \; \frac{\varepsilon_{ox}}{\varepsilon_S} \; \sqrt{\; \frac{2\,\varepsilon_S \; (\psi_S + V_{BG})}{q \; N_A} \; } \; \right) \, \hat{} \sim 0.5 \end{split}$$

tox:氧化物的厚度, cox:氧化物的電容率

L:通道長度, Vo:汲極電壓, Vbi:內建電位障礙

### 2-3 表面電位相關推導

前兩節我們已分別求得表面電位的一個代表值和臨限電壓的表示式。而現在我們要做的便是從另一個方向去推導表面電位詳細的表示式,進而使得分布在 MOS 表面各處的表面電位大小關係能清楚地顯現出來。

首先我們由 Poisson's equation 開始推導,

Poisson's equation :

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} = \frac{q}{\varepsilon_s} N_A$$

由此可導出一有關  $y_s$  的式子:

$$\frac{d^2 \psi_s}{dx^2} - A \psi_s = D$$

$$A = 4 \frac{e_{\text{Cox}}}{e_s} \frac{1}{t_{\text{Cox}} w} + \frac{6}{w^2}$$

$$D = \frac{q}{e_s} N_A - 4 \frac{e_{\text{Cox}}}{e_s} \frac{V_G}{t_{\text{Cox}} w} + \frac{6 V_{BG}}{w^2}$$

而接下來再利用我們已知的Ys 邊界條件:

$$y_s = V_{bi}$$

for  $x = 0$

$y_s = V_D + V_{bi}$  for  $x = L$

代入求解,最後可解得Ys的表示式:

$$\psi_{\text{S}} = -\frac{D}{A} + \left(V_{\text{D}} + V_{\text{bi.}} + \frac{D}{A}\right) \text{ Exp}\Big[\sqrt{A} \left(\mathbf{x} - \mathbf{L}\right)\Big] + \left(V_{\text{bi.}} + \frac{D}{A}\right) \text{ Exp}\Big[-\sqrt{A} \mathbf{x}\Big]$$

這就是在我們的專題中非常重要的式子。利用我們導出的這個式子,配合上先前已經求出的表面電位值、空乏區寬度和臨限電壓表示式,我們就可完整地繪出在臨限電壓時平行 MOS 介面的方向 (x 軸) 與表面電位的關係圖。

而且我們導出的ys表示式還能進一步導出其最小值ymin:

$$\overline{\psi_{min}} = -\frac{D}{A} + 2\sqrt{\left(V_D + V_{bi} + \frac{D}{A}\right)\left(V_{bi} + \frac{D}{A}\right)} \text{ Exp}\left[-\frac{\sqrt{A}}{2} \text{ L}\right]$$

然後將A與D之式子代入ymin 還能更進一步求出閘極電壓 Vg和 ymin 的關係式:

$$V_{G} = \overline{\psi_{min}} + \frac{t_{cx}}{\varepsilon_{cx}} \sqrt{2 \varepsilon_{s} q \, N_{A} \, \left(\psi_{min} + V_{BG}\right)} - 2 \left[1 + \frac{3 \varepsilon_{s} \, t_{cx}}{2 \varepsilon_{cx} \, w}\right] V_{e} \, \text{Exp}\left[-\frac{\sqrt{A}}{2} \, L\right]$$

不過由於我們討論的是在閘極電壓等於臨限電壓的狀況下,所以以上兩個式子並沒有用到,但還是有提出來的必要性,因為它們都與表面電位的討論有關。

## 2-4 表面電位之繪圖與探討

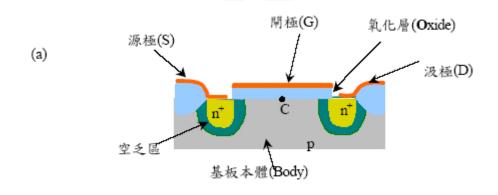

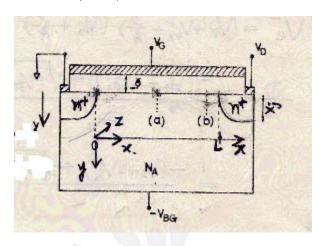

在這一節我們將把已求得的資料加以整合,來繪出表面電位的描述圖。圖 11 是一 MOSFET,我們即是要畫出在臨限電壓時,沿著 x 軸表面電位的變化圖。

#### 圖 11、一 MOSFET 之剖面圖

在資料整合時,會發現Ys的表示式中仍有未知的表面電位值及空 乏區寬度值,我們將在 2-1 節所求得之表面電位代表值以Ymin表示代 入,而其對應的空乏區寬度值以 w 表示代入,如此即可解決這個問 題。以下是用 mathematica 實際做出的程式及結果:

```

(*長度:cm,K為參考資料中之A,Q為D.此時VG=VT*)

\epsilon_{\text{CX}} = (3.9) (8.8510^{-14});

\epsilon_s = (11.7) (8.8510^-14);

L = 10^{-4};

V_{FB} = 0;

V_{RG} = 2;

t_{cx} = 2510^{-7};

q = 1.610^{-19};

N_{\Delta} = 10^{16}:

N_D = 10^19;

n_i = 1.510^10;

V_{t} = 0.0259;

V_{bi.} = V_t \text{Log}\left[\frac{N_A N_D}{n_i \wedge 2}\right];

\psi_{\min} = 0.6946403543025464;

w = 0.00005905680903653883;

\eta_0 = \frac{\epsilon_{ox}}{\epsilon_s} \frac{\sqrt{(V_D + V_{bi} - \psi_{min}) (V_{bi} - \psi_{min})}}{\psi_{min} + V_{BG}} \left( \frac{1}{t_{cx}} \sqrt{\frac{2 \epsilon_s (\psi_{min} + V_{BG})}{\sigma N_{b}}} + \frac{3}{2} \frac{\epsilon_s}{\epsilon_{ox}} \right);

l_0 = \sqrt{\frac{2 \varepsilon_s (\psi_{min} + V_{BG})}{q N_A}} \left[ \frac{3}{2} + \frac{1}{t_{ox}} \frac{\varepsilon_{ox}}{\varepsilon_s} \sqrt{\frac{2 \varepsilon_s (\psi_{min} + V_{BG})}{q N_A}} \right] ^{-0.5};

V_{T} = V_{FB} + \psi_{min} + \frac{t_{ox}}{\epsilon_{ox}} \sqrt{2 \epsilon_{s} q N_{A} (\psi_{min} + V_{BG})} \left[ 1 - \eta_{0} \text{ Exp} \left[ \frac{-L}{L_{0}} \right] \right];

K = 4 \frac{\epsilon_{OX}}{\epsilon_{S}} \frac{1}{t_{OX} w} + \frac{6}{w^2};

Q = \frac{q}{\epsilon_s} N_A - 4 \frac{\epsilon_{CX}}{\epsilon_s} \frac{V_T}{t_{CX} W} + \frac{6 V_{BG}}{W^2};

\psi = \text{Table}[\psi_{s}, \{V_{D}, 1, 5\}];

Plot[Evaluate[\psi], {x, 0, 0.0001}, AspectRatio \rightarrow 1.9/1, PlotRange \rightarrow {0, 6},

GridLines \rightarrow {Automatic, Automatic}, Frame \rightarrow True, FrameLabel \rightarrow {"x(cm)", "\psi_s(V)"}]

```

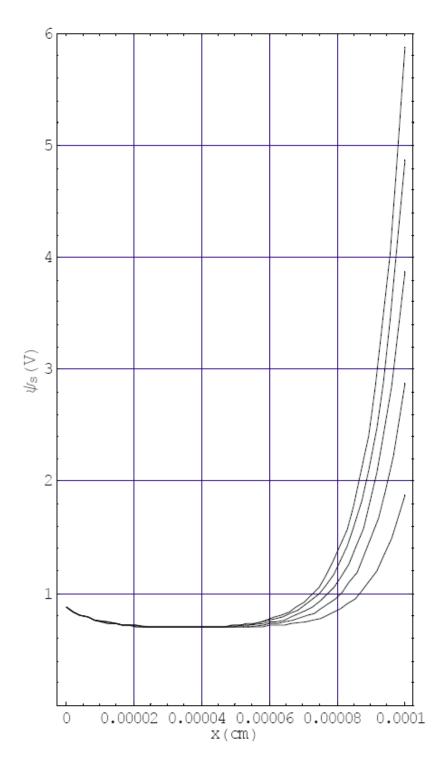

圖 12、表面電位描述圖(由下至上: $V_D 1V \sim 5V$ )

圖 12 是程式執行的結果,為在長度為 1  $\mu$  m 的通道中,表面電位變化之情形,由下到上的五條曲線是改變汲極電壓 (由 1V~5V)

的值所造成之結果。由此圖我們可知道,改變汲極電壓對表面電位所 造成的影響是在靠近汲極端的表面電位會受到汲極電壓之影響而大 幅上升,而通道中央及靠近源極的表面電位則是幾乎不受影響。

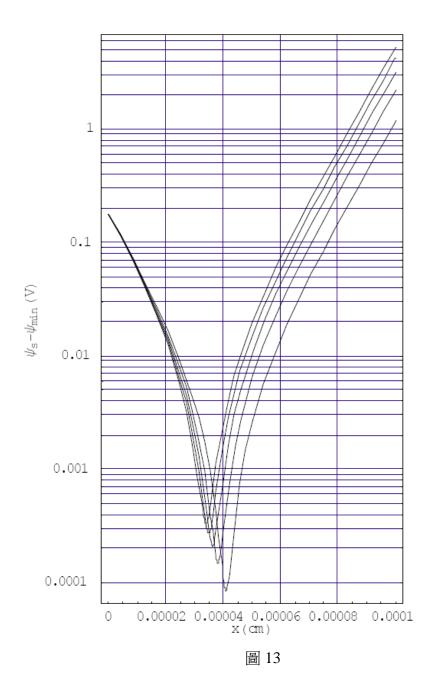

為了探討更多特性,我們將上述程式稍作修改,把表面電位Ув之表示式減去在2-1節所求得之表面電位代表值,再將圖的縱軸取對數來觀察。以下是用 mathematica 實際做出的程式及結果:

```

(★長度:cm,K為參考資料中之A,Q為D.此時V<sub>G</sub>=V<sub>T</sub>*)

<< Graphics `Graphics `

\epsilon_{\text{OX}} = (3.9) (8.8510^{-14});

\epsilon_s = (11.7) (8.8510^-14);

L = 10^{-4};

V_{FB} = 0;

V_{BG} = 2;

t_{ox} = 2510^{-7};

q=1.610^-19;

N_A = 10^16;

N_D = 10^19;

n_i = 1.510^10;

V_t = 0.0259;

V_{bi.} = V_t \text{ Log} \left[ \frac{N_A N_D}{n_i ^2} \right];

\psi_{\min} = 0.6946403543025464;

w = 0.00005905680903653883;

\eta_0 = \frac{\epsilon_{\text{CX}}}{\epsilon_{\text{S}}} \frac{\sqrt{\left(V_{\text{D}} + V_{\text{ki}} - \psi_{\text{min}}\right) \left(V_{\text{ki}} - \psi_{\text{min}}\right)}}{\psi_{\text{min}} + V_{\text{BG}}} \left[\frac{1}{t_{\text{CX}}} \sqrt{\frac{2 \epsilon_{\text{S}} \left(\psi_{\text{min}} + V_{\text{BG}}\right)}{q N_{\text{A}}}} + \frac{3}{2} \frac{\epsilon_{\text{S}}}{\epsilon_{\text{CX}}}\right];

\label{eq:loss_loss} \begin{split} \textbf{1}_0 = \sqrt{\frac{2\,\varepsilon_{\text{S}}\,\left(\psi_{min} + \,V_{BG}\right)}{q\,N_A}}\,\,\left[\frac{3}{2} + \frac{1}{t_{ox}}\,\,\frac{\varepsilon_{ox}}{\varepsilon_{\text{S}}}\,\,\sqrt{\frac{2\,\varepsilon_{\text{S}}\,\left(\psi_{min} + \,V_{BG}\right)}{q\,N_A}}\,\right] \,\text{$^{\circ}$-0.5;} \end{split}

V_T = V_{FB} + \psi_{min} + \frac{t_{ox}}{\epsilon_{ox}} \sqrt{2 \epsilon_s \, q \, N_A \, (\psi_{min} + V_{BG})} \, \left[ 1 - \eta_0 \, \text{Exp} \left[ \frac{-L}{l_0} \, \right] \right];

K = 4 \frac{\epsilon_{OX}}{\epsilon_{S}} \frac{1}{t_{OX} w} + \frac{6}{w^{2}}

\label{eq:Q} \text{Q} = \frac{q}{\varepsilon_\text{S}} \; N_\text{A} - 4 \, \frac{\varepsilon_\text{CK}}{\varepsilon_\text{S}} \; \frac{V_\text{T}}{t_\text{CK} \, w} \, + \, \frac{6 \, V_\text{BG}}{w^2} \; ;

\psi_{\text{S}} = -\frac{Q}{\kappa} + \left(V_{\text{D}} + V_{\text{bi}} + \frac{Q}{\kappa}\right) \text{ Exp} \left[\sqrt{K} \left(\mathbf{x} - \mathbf{L}\right)\right] + \left(V_{\text{bi}} + \frac{Q}{K}\right) \text{ Exp} \left[-\sqrt{K} \mathbf{x}\right];

\psi = \text{Table}[\psi_s - \psi_{\min}, \{V_D, 1, 5\}];

LogPlot[Evaluate[ψ], {x, 0, 0.0001}, AspectRatio → 1.9/1, GridLines → {Automatic, Automatic},

Frame \rightarrow True, FrameLabel \rightarrow {"x(cm)", "\psi_{s}-\psi_{min}(V)"}]

```

圖 13 是程式執行的結果,從此圖我們可以看出,減去在 2-1 節用理論所求得之表面電位代表值後,圖上的電位仍然全大於 0,這表示我們用理論所求得之表面電位值是表面電位的最小值。而且約在圖中通道中心的位置電位最小,幾乎接近 0,在扣除因實驗所可能產生的誤差後,我們可以知道約在通道中心的位置表面電位最小,而且就是我們用理論 (ys=2fp) 所求得之表面電位值。

# 三、MOS 通道二維電位描述

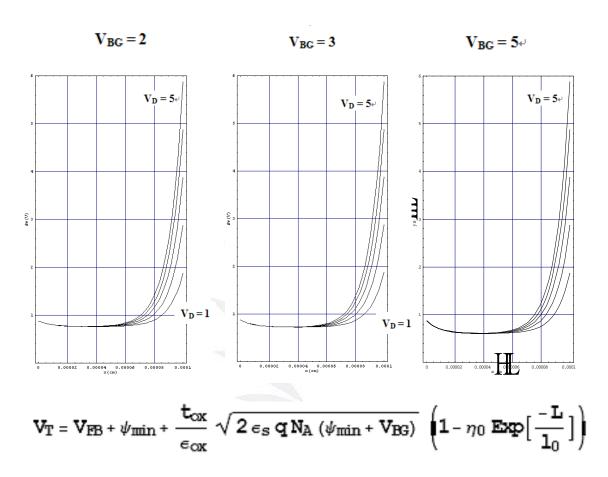

### 3-1 改變 VG

所以隨著 VBG 的增加,臨限電壓跟著上升

當 VT=VG 時進入反轉區,反轉區的反轉條件為

表面電位

$$\Phi \min + VBG = 2 \Phi fp$$

所以當 VBG 的增加表面電位  $\varphi$  min 會隨之減小

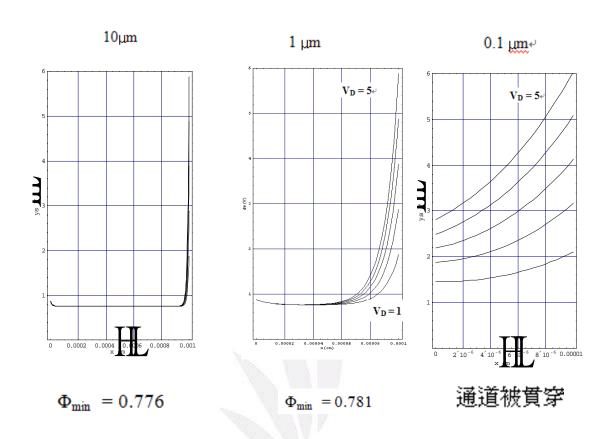

### 3-2 改變 L 對表面電位的影響

在N通道中,當通道長度減少時,在通道區域被閘極控制的電荷 比例則會減少,而當汲極電壓增加時,空乏區會延伸到通道區中,所 以閘極控制的本體電荷 Q'SD(max)會越來越少,

$X VT = (-Q'SS)(tox/ \varepsilon ox) + \varphi ms + 2 \varphi fp$

所以當通道長度變小臨限電壓會著縮小,可是當通道尺寸太小時,會產生通道貫穿的現象,此時的各處表面電位會有大幅上升,不 止有在汲極端才會上升的現象

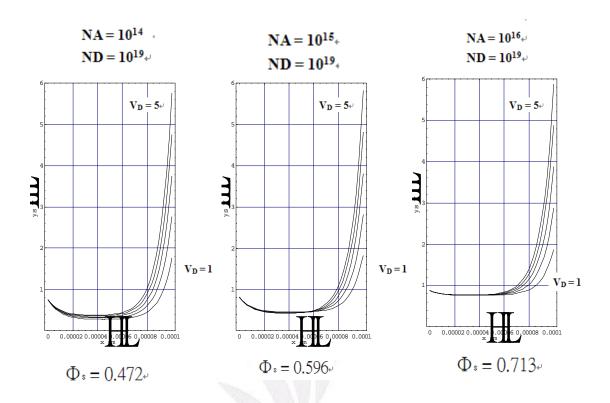

## 3-3 N通道改變 NA 掺雜量

之前我們已經做了在臨限電壓時,MOS 的表面電位跟通道位置的關係圖;還有在某一通道位置上,從表面至基板的垂直方向電位變化圖。而現在我們就要將兩者結合起來,製作 MOS 垂直切面之電位變化圖,即像圖 11 般的 MOSFET 剖面圖,剖面上的電位變化圖。以下是用 mathematica 實際做出的程式及結果,而原本沒設定的汲極電壓一率設為 3V:

# 第五章 結論

MOS 的表面電位以往在半導體物理之中通常以一未知數或常數就輕鬆帶過,這次專題探討後才了解,當仔細了解並實際以可變參數代入公式,以 MATHEMATICA 做圖分析後,顯示出實際上更為細微的結果,並告訴了我們表面電位並非定值,而是隨著代入參數的不同而有所變化,且讓我們知曉這些數據並不是可以隨便決定的,而是有更多的實驗做根據.

在實驗中,我們可以發現當改變汲極電壓和改變通道長度對表面電位的影響,及其他外在因素所可能會造成的改變,也使我們粗略了解到目前業界為何以小尺寸元件為競爭的標的.

於實驗中,為了順利模擬出公式的推導,閱讀了不少有關MATHEMATICA 的參考書,於其中獲益良多,也驚訝於其軟體的強大,希望以後能有機會再多多琢磨,並能將這次的經驗發揮到其上,也讓專題多出了額外的收穫。

# 参考資料

- 1.IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-26, NO.4, APRIL 1979, PAGE 453~460.

- 2.書名:Semiconductor Physics & Devices,作者:Donald A. Neamen PAGE519~600.

- 3.Kano, K. Semiconductor Devices. Upper Saddle River, NJ: Prentice Hall, 1998.

- 4. Yang, E.S. Microelectronic Devices. New York: McGraw-Hill, 1988.